So I have a pair of Avocent DSR4010s (16-port IP KVM boxes). I can only use them as local KVMs because you can only connect to them via their DSView management software, which is super proprietary and you can& #39;t even get licenses for the old versions anymore. So let& #39;s look inside!

First thing to note: there is a lot of hardware in here. That& #39;s the top board of two; it contains one big CPU and four video processing chains consisting of an ADC, a scaler/video processor, and an FPGA each. Each has its own RAM and flash. The bottom board is mostly analog.

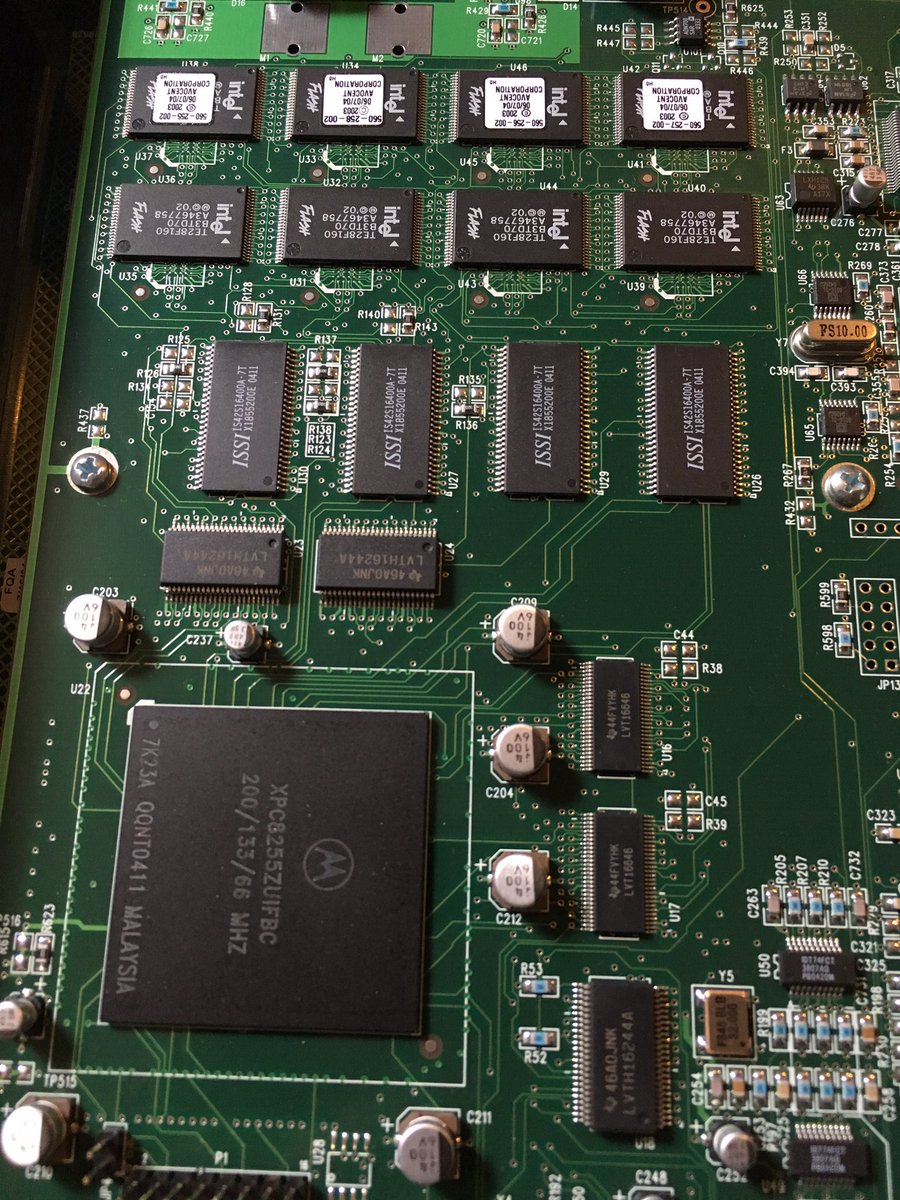

Here& #39;s the CPU. It& #39;s an early MPC8255 PowerQUICC II, which is a very beefy communications-oriented PowerPC SoC that has a dedicated communications coprocessor (that& #39;s the QUICC). It seems like overkill here, but it was a good embedded PPC. Note: XPC are early run MPC chips.

The CPU has a normal amount of RAM and flash attached; I& #39;m assuming the filesystem mounts directly from the flash. Note that it& #39;s a 4-chip-wide interface, so it& #39;s most likely a 64-bit local bus (which, if it& #39;s attached directly to the 60x bus, makes sense).

(more tonight as I get a chance to post the pictures, making dinner now)

Ok, took longer to get a time slice than I thought. Here goes...

Here& #39;s two copies of the video chain. This has an AD9884 video frontend (fancy triple ADC meant for video capture), a PW164A video processor, and a FLEX10K50 FPGA. The FPGA has 8 MB SDRAM, 128KB SRAM, and some flash (unknown size, but probably 2MB) attached.

Note that the SDRAM chips are the same as those used on the PowerPC, and it& #39;s a good bet that the flash is as well; this is a good way to simplify design and keep BOM costs down, even if the part might be overkill somewhere.

This is between the CPU and the front panel. There& #39;s a medium-sized Altera CPLD there (not sure what, but I recognize the edges of the text that peeks out under the label). This is likely used for programming the FPGAs from their flash using the Fast Parallel Programming mode.

You& #39;ll also note the 2x5 header next to the CPLD, which is probably the CPLD JTAG port (Altera uses a 2x5 header), as well as the 2x8 header which looks a lot like Motorola& #39;s JTAG-COP header for debugging this generation of PowerPCs. I& #39;ll have to try those later.

In the upper left hand corner here by the FPGA, you can also see depopulated 2x5 headers, which are individual JTAG headers for the FPGAs (I checked, the visible traces match up). I can imagine a few reasons why they might not have wanted to make the entire board one long chain.

Fun fact about the FLEX10K50: it was a fairly medium-large FPGA of its time. It had 2880 Logic Element and 20Kbits of on-chip RAM; this is dwarfed by even the smallest Cyclone III 3C5 now (considered long in the tooth) at 5K LEs and 414Kbits of SRAM (plus a 23 18x18 multipliers).

The purpose of the FPGAs isn& #39;t clear to me yet; my assumption is that they do a combination of light video compression (which they& #39;re really proud of in their advertising copy for this thing) and marshaling the video data for better consumption by the PowerPC& #39;s bus.

The other interesting thing about the video chains is that there are only 4 of them (I haven& #39;t taken the top board off yet, but peeking under I don& #39;t see any on the underside). There are 16 inputs. Presumably, then, there& #39;s a 16x4 analog video matrix switch on the lower board.

Here& #39;s another interesting thing; there& #39;s some sort of depopulated header at the end, too. Some of the traces go to flash pins, others look like power. I& #39;m not sure what this is for, but my money would be on either a breakout for a logic analyzer or a connection to a slave board.

Check back again later when I& #39;ve had the chance to take off the top board and see what& #39;s underneath! After that, when I have some real cycles to spare (hahahaha, maybe next year?), I& #39;ll hook up some JTAG cables and see if I can find anything fun.

My main goal here, other than just curiosity, are to figure out how to connect to this beast over IP without having to run and license DSView 3. A working JTAG connection would let me dump the flash easily from the PPC (less so for the FPGAs, but We Have Ways To Make Them Talk).

I was dumb and accidentally started a new thread, so please continue here. https://twitter.com/6502_ftw/status/984973013102755840?s=21">https://twitter.com/6502_ftw/...

Read on Twitter

Read on Twitter